苹果想带「王炸芯片」参观侏罗纪公园 | 硬哲学

关于苹果的自研芯片 M1 系列仍然有着许多谜题。

也就在最近,关于 M1 芯片的后续,M2、M3 的传闻纷沓至来,不过多是一些捕风捉影的信息,对于架构、性能、核心这些都没有特别明确的信息,而更多的是围绕台积电工艺节点的升级。

▲ M1 还没出完,M2、M3 或许就要来了. 图片来自:progamer

台积电 4nm、3nm 等新的制程工艺可能会是较大的升级点。如此来说,在能耗比上已惊艳众人的 M1 系列,M2、M3 只增不减。

只是,在两年后,当节点工艺升级到 3nm 之后呢?

大概有两条,一条是把节点工艺干到 1nm,无线逼近物理极限,但难上加难。另一条是绕过节点工艺升级带来的福利,走 Chiplet「小芯片」之路。

一颗 M1 Max 不够?那就给 Mac Pro 装上两颗

不过,一向不喜欢被供应链摆布的苹果,在吃节点、ARM 芯片高能效比优势的同时,或许也在找可行之法。

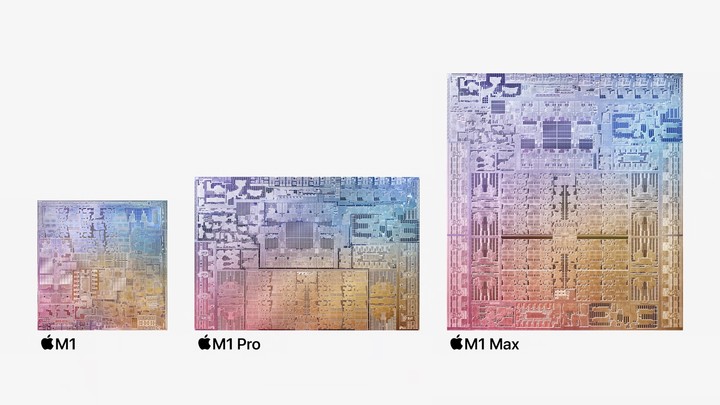

从 M1 到性能更强的 M1 Pro、M1 Max,它们有着几乎相同的架构,单核心的性能释放较为接近,最大的不同其实是在核心数目上。

甚至,你也可以简单的理解为,基于 ARM 的 M 芯片是靠着堆核心数目来获得更高的性能天花板。

- M1:CPU 4+4 核,GPU 8 核,160 亿晶体管,16 核心神经网络;

- M1 Pro:CPU 2+8 核,GPU 16 核,337 亿晶体管,16 核心神经网络;

- M1 Max:CPU 2+8 核,GPU 32 核;570 亿晶体管,16 核心神经网络;

而简单的从另一个维度来看,M1 芯片面积约 120mm²,M1 Pro 为 245mm²,到了 M1 Max 这里就直接飙升到 432mm²。

同一代 M 芯片,越 Max,核心数、芯片面积也就越 Max,从这里也不难理解苹果对 M 芯片的命名规则了,通俗易懂,微软、Intel、高通真的该好好学学。

虽然苹果芯片架构师、副总裁蒂姆・米勒特(Tim Millet)早在 11 月份就在 Upgrade 播客里详细的阐述了苹果研发 M 芯片的辛路历程,但对于 M 芯片接下来如何发展,以及在 Max 基础之上如何更 Max 只字未提。

▲ 苹果芯片架构师、副总裁蒂姆・米勒特(Tim Millet). 图片来自:Apple

随着 MacBook Pro 14/16 陆续上市,经过许多民间 DIYer 的探究,似乎也发现了苹果让 M1 Max 更 Max 伏笔。

那就是「放两个 M1 Max 进去,甚至还可以加倍」。

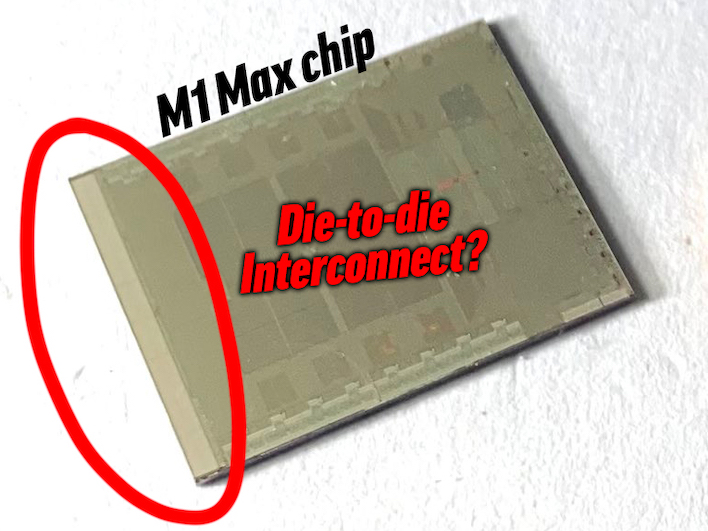

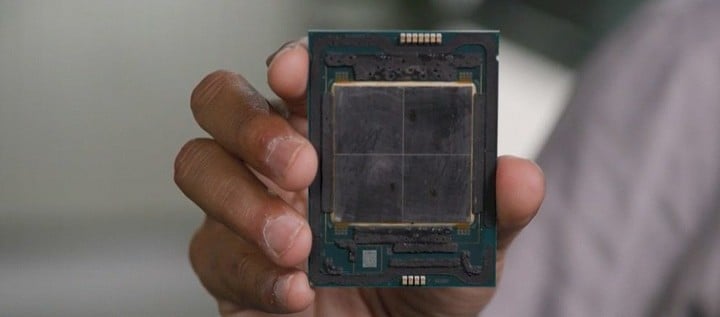

▲ M1 Max 隐藏区域. 图片来自:HothardWare

这个猜想实则是基于拆解后,发现 M1 Max 相对于 M1 Pro 多出了一块「不明区域」,脑洞一番之后,猜测是为连接两颗甚至多颗 M1 Max 预留的「高速总线」。

▲ Tim Cook:Intel,this is for you. 图片来自:Max Tech

这也契合了此前新 iMac Pro、Mac Pro 会采用多颗 M1 Max 组成的超大颗处理器的传闻。「这简直就像是在玩乐高、堆积木,简直乱拳打死老师傅」。

不过,「堆积木」这个说法并不太准确,「拼图」更精准一些。如此来说,双份 M1 Max 的芯片面积会相当可观,四倍那就更前无古人了。

M1 Max Duo 超过英伟达的顶级 GPU GA100 芯片面积(826mm²)几乎板上钉钉。

如此巨大的 SoC,纵观整个半导体历史,绝对能够算上「霸王龙」级别的芯片,更别说它会基于 5nm 工艺,成本也极有可能超过任何一枚当代的芯片。

当 M 系芯片走进「侏罗纪公园」

从重达 30 吨,占地 170 平方米的初代计算机 ENIAC,到现在的桌上 PC,设备几乎都朝着小型化、集成化发展。

而半导体世界的处理器也是如此,当工艺节点还属于 μm 时,英特尔初代奔腾(Pentium)面积大概是 294mm²,基于 0.8μm 工艺。

▲ Intel Pentium III Xeon.

在 x86 处理器时代,Intel Pentium III Xeon 面积达到 385mm²,基于 0.18μm 工艺。但在当时,众处理器厂商在严控体积打压成本推出较为平价的 PC 以推向大众。

后续,无论是 64 位的普及,还是工艺节点的跃升,处理器的尺寸多是控制在 500mm² 以下,成本控制,高效利用晶圆的前提下,几近遏制住了消费级处理器面向「恐龙化」的发展。

消费半导体行业似乎也逐步从侏罗纪慢慢走向了新时代。

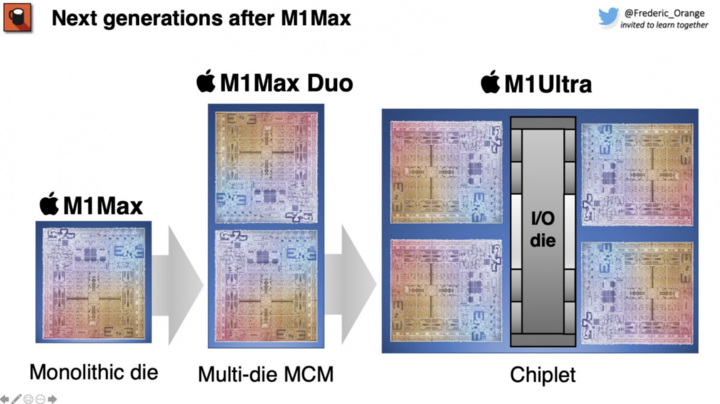

▲ 民间大神也在为苹果 M 芯片的发展之路出谋划策. 图片来自:Twitter

而此时苹果 M 芯片可能的发展路线似乎又绕回到了「侏罗纪」,只不过处理器尺寸跃进的同时,晶体管的密度也没有落下。

虽然听起来将两枚芯片拼在一起应该不难,也无需重新设计架构、核心。但实际之中,随着芯片面积的增加(尤其是成倍的增长),以及保证足够良率和产能的情况下,成本直接起飞。

而苹果的 M 系芯片依然是个消费级产品,一年前摆脱 Intel,一方面是为了控制产品力,另一方面其实还是控制成本,达到利润最大化。大面积 SoC 飘忽不定的成本显然不是苹果所期望的。

▲ M1 Max 最高的统一内存是 64GB,那 M1 Max Duo 直接来到 128GB?

另一方面,两枚或者更多的 M1 Max 拼接,统一内存(UMA)的设计也会是一个巨大的难题,重新规划多核心的位置,引入更大的带宽,以及更高容量的内存再所难免。

于公,可能是更复杂的芯片设计,于私,可能会无形增加几倍的成本,都会是苹果 M 芯片变得更 Max 的两大绊脚石。

摩尔定律已成过去,日拱一卒才是当下

「集成电路上可容纳的晶体管数目,约每两年会增加一倍。」这是著名的摩尔定律,它还有另外一个说法,「每隔 18 个月,芯片的性能就会提高一倍。」

▲ MacBook Pro 16. 图片来自:dpreview

这里的性能其实就指的是晶体管数量,M1 Max 相较于 M1 有着 3.5 倍的性能提升,恰恰也正好反应的是晶体管数量的差距。

晶体管数量翻倍在 M1 系列这里,是芯片面积增加。而从历史来看,更多依靠的还是工艺上的进步,从 μm 到 nm 级,晶体管数量也从百万级跃升到亿级。

但是在 2013 年左右,摩尔定律就有所放缓,从彼时到现在,工艺节点的提升对于性能的收益正在不断减少。

更先进的工艺制程,的确可以翻升晶体管数量,但也伴随着成本和良率的变化。

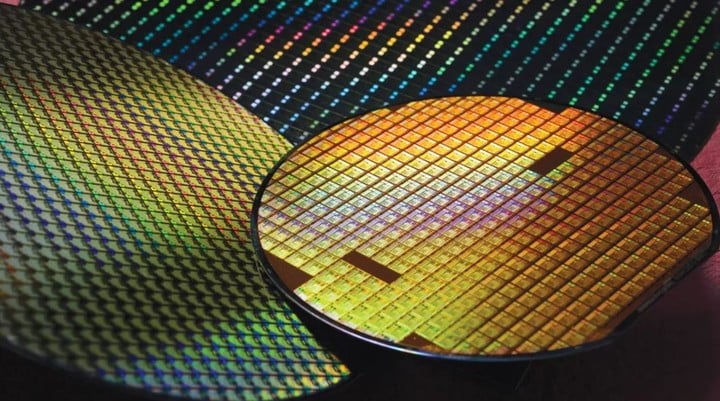

▲ 台积电预计 2023 年开始投产 3nm 工艺. 图片来自:anandtech

根据国际商业战略公司 (IBS) 所公布的数据,设计 3nm 芯片预计将耗资 5.9 亿美元,而 5nm 只要 4.16 亿美元,7nm 为 2.17 亿美元,28nm 不过才 4000 万美元。

台积电此前对外宣布将会投资 200 亿美元来兴建 3nm 晶圆工厂,同样是为了 3nm,三星所耗费的并不比台积电低。

而到目前为止,也只有台积电和三星在积极布局 3nm 晶圆,其他厂商并非是不想,只是花不起这钱。

另一方面,芯片的良品率随着面积增大而降低,700mm² 的设计合格率大概只有 30%,缩小到 150mm² 良品率就飙升到 80%。

无论从哪方面来看,芯片升级之路似乎已经被堵死了。

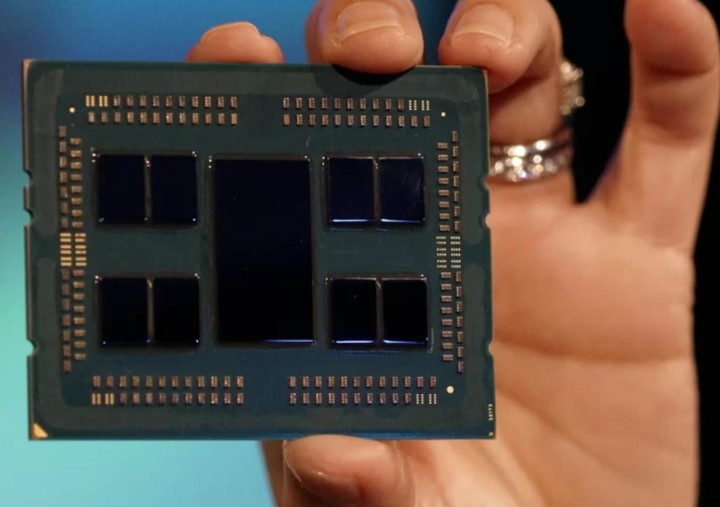

▲ AMD 基于 Zen 2 的 EPYC 2 (Rome) 处理器. 图片来自:AMD

为了能继续提升芯片规模和密度,不少人把目光从工艺节点的升级转向了封装工艺上,也就是 AMD 押宝的 Chiplet(小芯片)技术。

Chiplet 简单来说就像汤圆馅的饺子一样,把不同功能的小芯片封装在一起,而不是直接从晶圆上切割,以先进的封装工艺来弥补工艺节点的停滞。

▲ 目前对于 Chiplet 最为形象的比喻(但我不认可这种吃法).

近年来 AMD 也正是通过 Chiplet 技术不断地提升处理器密度对 Intel 进行了逆袭,逐步开始抢夺市场。

对于近年崛起的 Chiplet,科技行业权威咨询机构 The Linley Group 在《Why Big Chips Are Getting Small》一文中,直接提出 Chiplet 可以将大型 7nm 芯片的设计成本降低 25% 以上,而在面对 5nm 和更高工艺时,节省的成本还会更高。

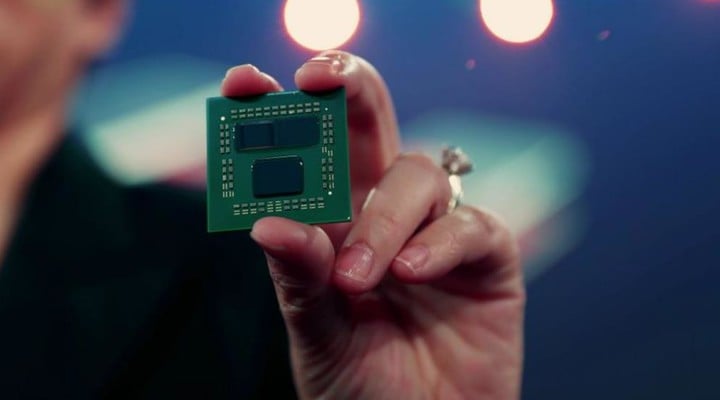

▲ AMD 基于 3D Chiplet 封装的 Ryzen 9 5900X CPU.

而 AMD 所公布的 3D V-Cache 也在证实,旧的工艺与先进的封装工艺所结合的 Chiplet,可以达到更高节点的性能,甚至还能把不同工艺节点的芯片进行混装,有着足够的灵活度。

除了降低成本,实现更先进的性能之外,Chiplet 还会加快产品面市速度,毕竟直接利用旧芯片配合先进封装工艺即可,甚至完全可以忽略对先进工艺节点的布局。

说了这么多好处,Chiplet 也有相应的劣势,小芯片 2D、3D 的堆叠对热管理设计有着相当高的要求,且封装体内总热功耗会有明显的提升。

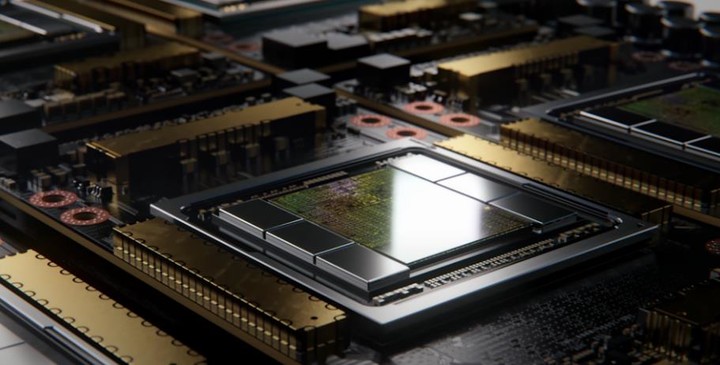

▲ 基于 Chiplet 的 Intel 服务器芯片. 图片来自:nextplatorm

但无论如何,Chiplet 已经被很多机构、厂商认定为后摩尔时代,在芯片上性能持续突破的重要技术。

▲ M1 inside 的 Mac mini 与 MacBook Air.

而回到最开始的苹果自研 M 芯片上,通过 ARM 架构,以及工艺节点的升级,不断提升能效比,顺便控制下良率与成本。至于是否会通过拼接多个 M1 Max 一同组成复杂的巨型 SoC 塞入工作站级别的 Mac Pro 中,从目前来说,苹果有足够的的资本与实力去设计与生产出类似于「史前巨兽」的处理器。

▲ iMac Pro 2022 的非官方渲染图.

至于 Chiplet,我想它肯定已经出现在苹果芯片团队中的图纸上,与其面对未来不明朗的工艺节点提升,倒不如主动求变,凭借现行的 M 芯片、A 芯片去组合完成更深层次的 SoC 升级。